ahczgy

March 13, 2024, 1:04am

1

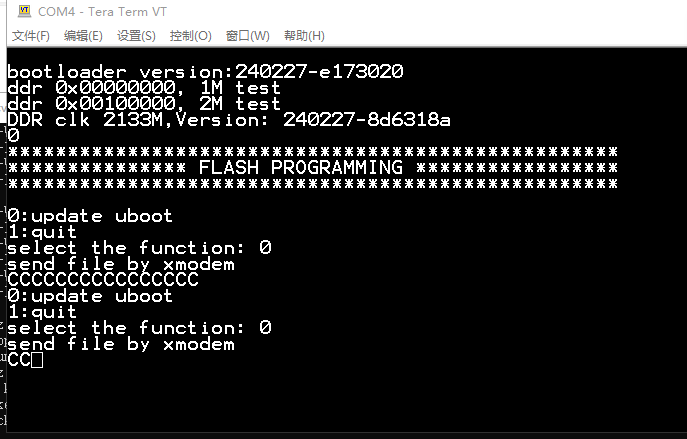

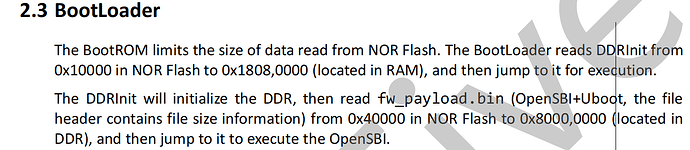

1、目的:兴趣,本人74年,有生之年只想在riscv硬件上真实跑个小系统,自己能明明白地知道它怎么运行的,能够修修补补,退休后有所乐,真心不想跑在qemu上。本来想跑在StarFive2上,然能力不足,突破不了uart模式下加载32K的大小限制,偶然发现VisionFive v1下有更好方式加载运行xv6内核,依据“JH7100 Boot User Guide,Version: V1, Date: 2021-09-30”的

2、运行情况

3、主要修改地方

(1)kernel/memlayout.h加上

(2)kernel/uart.c中

UART0改为UART3。

4、问题

运行到main.c时会出现莫名其妙错误,全局初始化变量started在mhartid=1核上会看到意想不到的值,后面全局变量都有同样的问题。

抱歉将VisionFive v1下的问题发在V2论坛里。

哥哥好雅兴。

尤其是 riscv 设计上就给系统层面做了分层。操作系统不是最上层。而且似乎还不是第二层,而是第三层。导致启动一个系统异常麻烦。以前的那些“裸硬件编程”的理解全都不好用了。

ahczgy

March 14, 2024, 9:55am

3

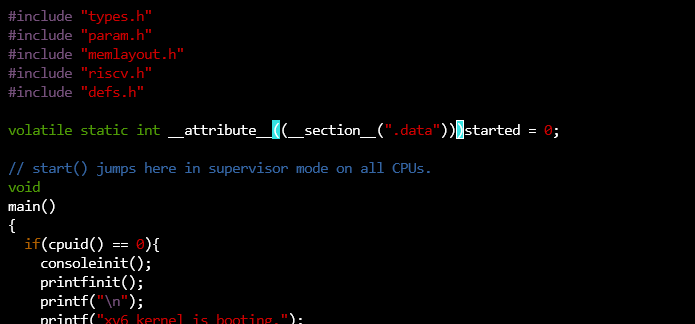

#include “types.h”#include “param.h”#include “memlayout.h”#include “riscv.h”#include “defs.h”

volatile static int started = 0;

// start() jumps here in supervisor mode on all CPUs.

scheduler();

估计是.bss段没有清零导致的。把started放到.data段试一下,比如

volatile static int started __attribute__((__section__(".data")));

如果没问题了那基本就是这个问题。那么你这个kernel要考虑到给自己的.bss清零的问题。上一个阶段的bootloader只会把你的kernel按照binary的方式加载,它不会管你后面的事情

1 Like

ahczgy

March 15, 2024, 12:35am

5

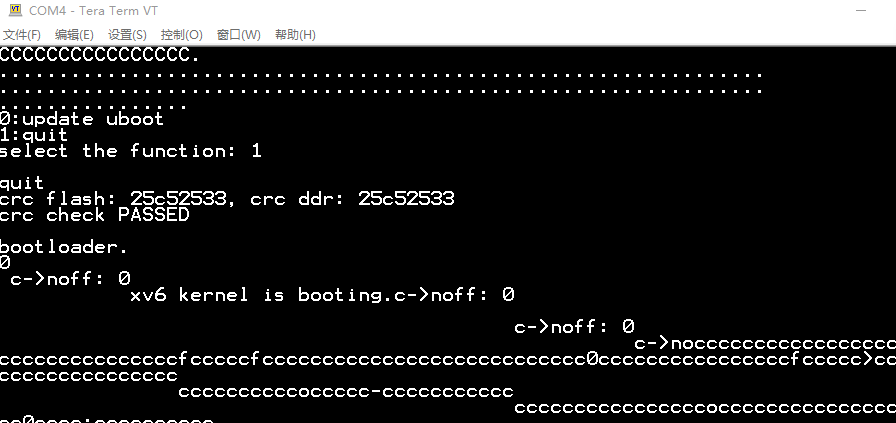

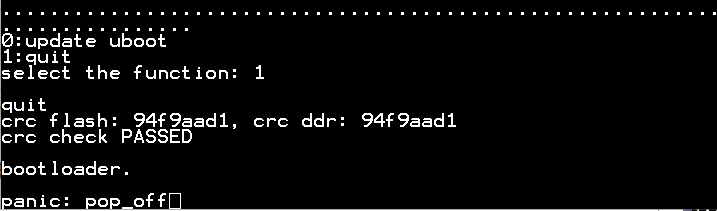

感谢,正如你所言解决了这个问题。

修改后:

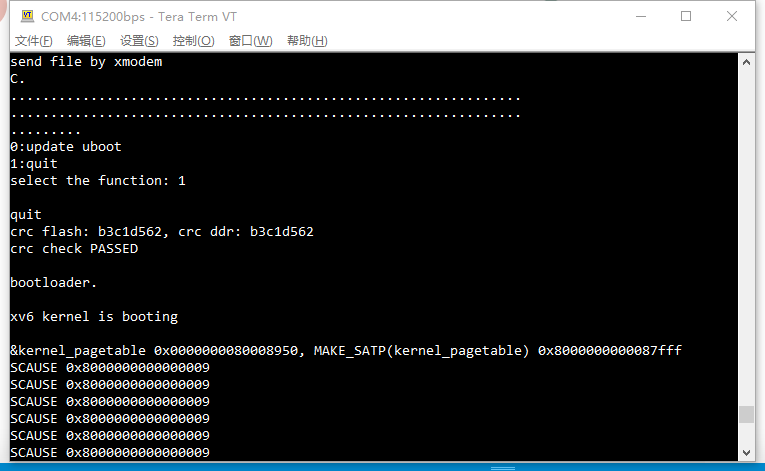

运行如下:

感谢!再学习加载与链接。

1 Like

ahczgy

March 19, 2024, 10:44am

6

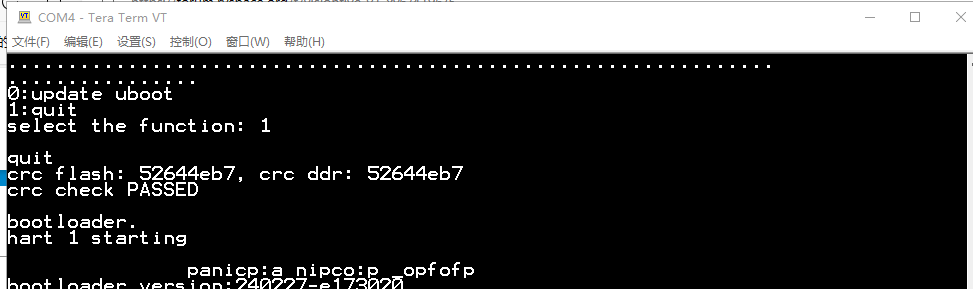

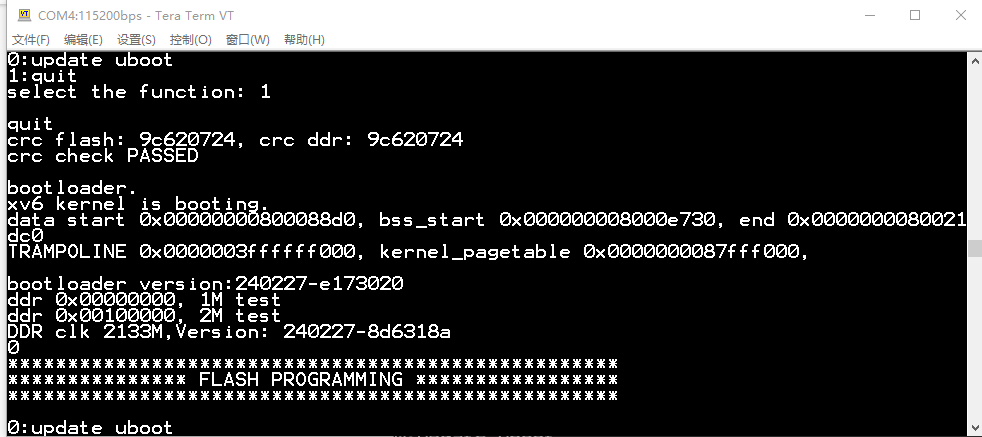

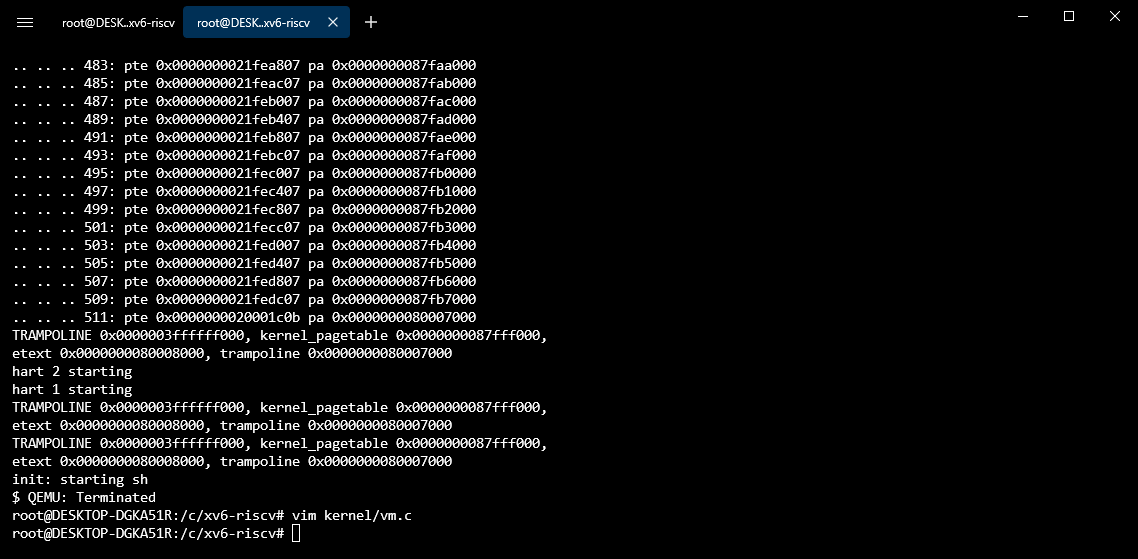

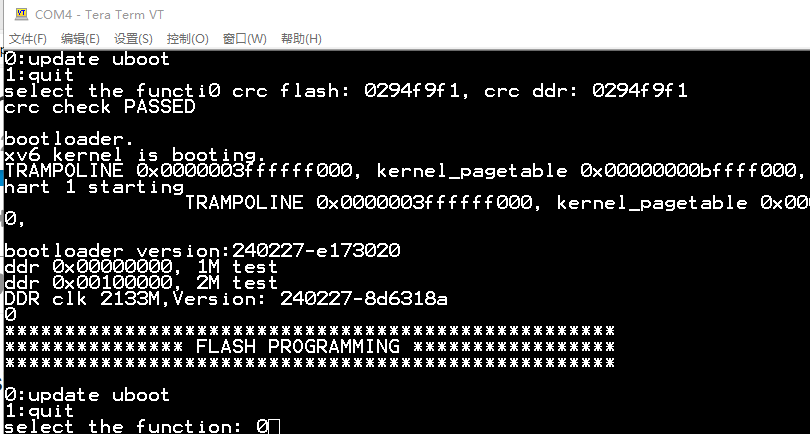

1、进展:uart3显示问题已解决。运行如下:

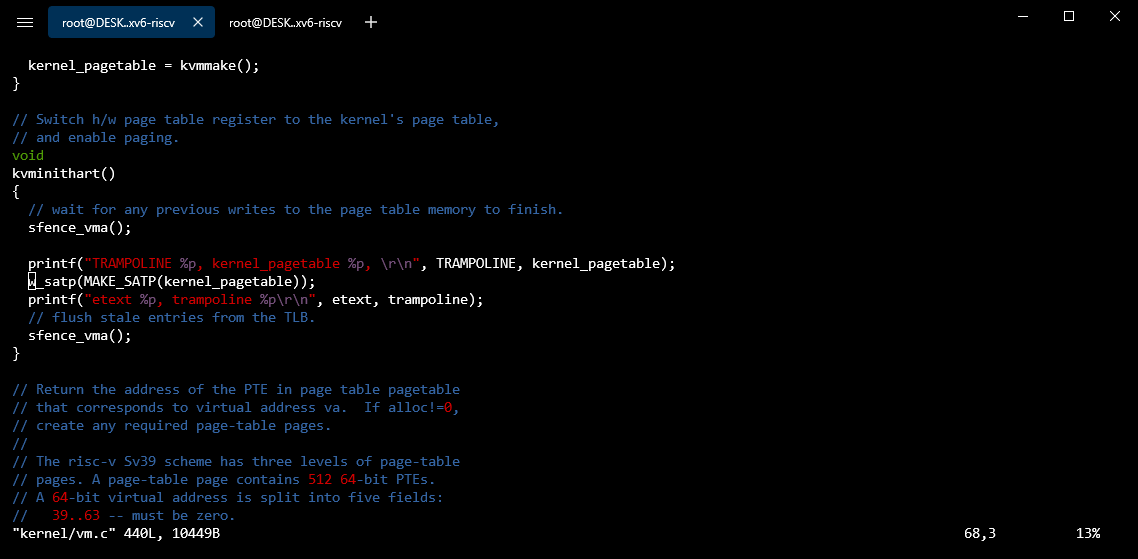

分页前后加了printf打印信息:

2、问题:分页后崩溃,已反复看了很多遍分页相关代码,没有看出问题,也查阅了《RISC‑V指令集手册,卷II:特权架构,版本1.10》 PMP、PMA和sv39分页相关章节,找不到问题所在,没有方向,请路过的大侠们指导一下,感谢!

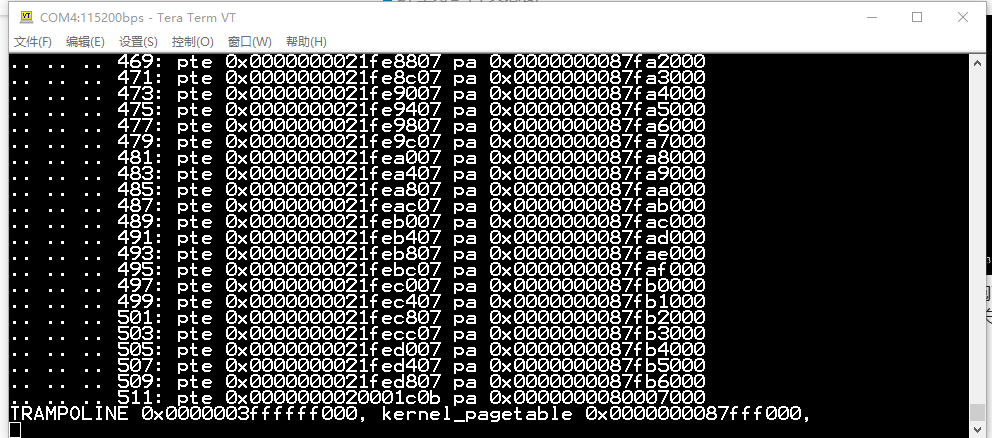

打印了内核页表内容,节选后面部分:

和qemu下运行内核页表比较:

略有不同。

ahczgy

March 20, 2024, 2:45am

7

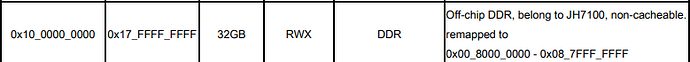

查看“JH7100 Data Sheet V01.01.04-EN (4-21-2021)”中Table 6-1 U74-MC Memory Map,这段:

与这段

上两段意思是:从0x008000_0000开始的32G内存是由0x10_0000_0000映射过来的,且无cache。

问题:xv6内核执行w_satp(MAKE_SATP(kernel_pagetable))分页时,会不会打乱上面的映射呢?刷新TLB时会不会也产生同样的问题呢?

注:Memory attributes: R - Read, W -Write, X - Execute, C - Cacheable, A - Atomics。

这个映射是在硬件实现的,目的是把DDR映射两遍,80000000开始的是正常的cacheable,1000000000开始的是不经过cache的,主要是为了方便写driver给那些非缓存一致性的设备。这里可以不用关心,把80000000当作DDR起始就行。我觉得不是这个映射的问题。首先得确认在JH7100里面你的xv6运行在什么模式下,应该是M模式,因为你是直接从ROM引导的,还没有加openSBI。那么就出问题了,看起来这个内核期待运行在S模式。而QEMU默认是会帮你把openSBI都加载好的,可以直接引导。所以你要么自己实现一个简单的sbi,或者你需要自己build openSBI,然后把xv6当作openSBI的FW_PAYLOAD,在build阶段嵌入到openSBI里面,然后再用ROM加载最终的fw_payload.bin

ahczgy

March 20, 2024, 7:10am

9

感谢解答。

4、运行路径:BootROM->SecondBootLoader->DDRInit->xv6;

5、xv6中有类似的sbi实现。

ahczgy:

4、xv6实现有类似的一个简单sbi。

OK 那么你的control-flow就和QEMU不一样了。那么你直接用qemu -bios xv6.bin启动qemu,然后看一下。这样qemu也是用M mode启动xv6,会尽可能接近jh7100的行为

ahczgy

March 21, 2024, 11:56am

13

sv39分页,真的搞不定了,感觉没什么,可就是不行。有没有大佬可指导一下,u74下sv39分页,感激不尽!!

ahczgy

March 24, 2024, 5:22am

14

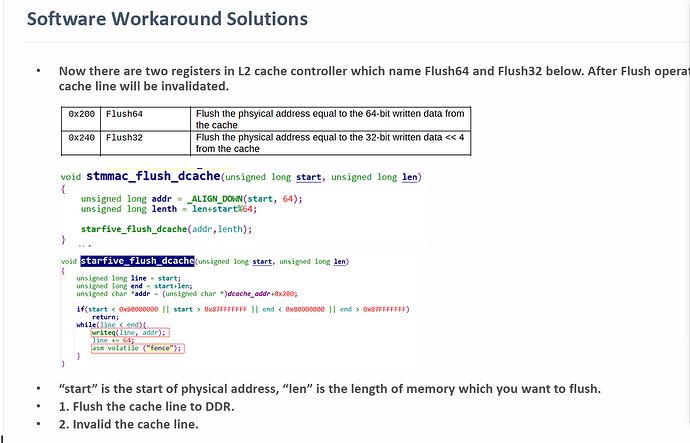

在“Memorandum -L2 Cache Coherence”文档有说明Root causes - L2 Cache Coherence (JH7100 SOC)问题,并给出解决办法如下:

1、这个是造成分页不成功的原因吗?

2、上图代码中的dcache_add是什么,对DDR内存来讲就是0x1000000000?

感谢大佬解答下。

应该不是。你xv6从jh7100 M模式启动,此时cache controller还没有enable。xv6估计也不会去enable

DDR内存被map两次,一次是通过cache controller,一次是bypass cache controller。这个offset就是两个的offset,换言之你可以通过给一个内存地址加上这个offset直接绕过cache controller访问DDR。

我觉得因该不是这个问题。改一下xv6 M模式的部分,在遇到exception的时候把exception打印出来看看

1 Like

ahczgy

March 25, 2024, 11:45am

16

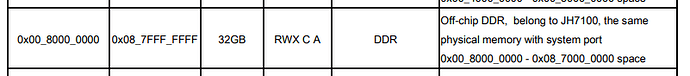

已查到dcache_addr出处"SiFive U74 Core Complex Manual"中的L2 Cache Controller:

ahczgy

March 25, 2024, 12:14pm

17

感谢解答。

1、xv6没有做cache controller的enable;xv6是从Qspi模式启动的,启动前的ScondBoot和DDRInit有没有做过呢?分页前要不要做cache controllerr的enable?

这是S模式下的外部中断,

等一下,你xv6具体改了那些东西?有没有一个你的repo给大家看一下你现在的xv6代码?

ahczgy

March 26, 2024, 9:06am

19

[quote="ganboing, post:18, topic:4196, full:true"]

等一下,你xv6具体改了那些东西?有没有一个你的repo给大家看一下你现在的xv6代码?

https://github.com/ahczgy/xv6vf1.git。基本没改

破案了,原因是U74的MMU行为和QEMU的MMU是不一样的,xv6根本没有考虑到这种情况

Two schemes to manage the A and D bits are permitted:

• When a virtual page is accessed and the A bit is clear, or is written and the D bit is clear, a page-fault exception is raised.

For non-leaf PTEs, the D, A, and U bits are reserved for future use and must be cleared by software for forward compatibility. It is important to note the U7 does not automatically set the accessed (A) and dirty (D) bits in a Sv39 Page Table Entry (PTE). Instead, the U7 MMU will raise a page fault exception for a read to a page with PTE.A=0 or a write to a page with PTE.D=0.

本质上就是PTE_A和PTE_D是用来跟踪使用过的page,不过U7不会自动更新这两个bit,而是让软件来维护。所以你xv6需要把 leaf-PTE 全部都加上PTE_A | PTE_D 不然直接就page-fault寄了

1 Like