Milestone Achievement: StarFive JH-7110 Successfully Passes RISC-V Architecture Test

StarFive JH-7110 passes the RISC-V Architecture Compatibility Test

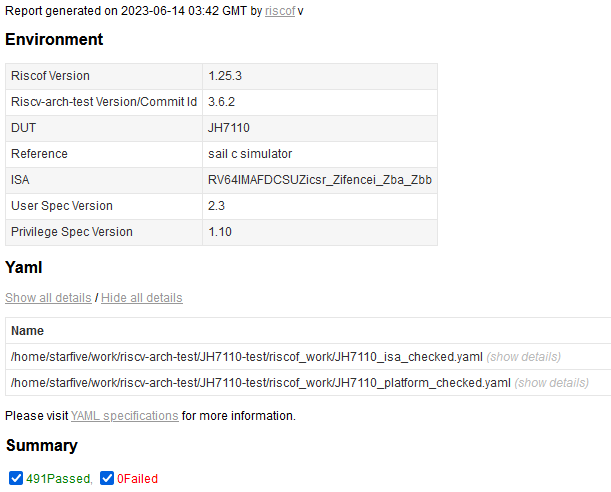

StarFive is proud to announce the successful upload of the RISC-V Architecture Test report, indicating that the design of JH-7110 fully complies with the RVI20 specification requirements. You can find the report at the following link: riscv-non-isa/riscv-arch-test-reports (github.com).

RISC-V Architecture Testing serves as our fundamental screening tool, ensuring that software written for specific RISC-V configurations or specifications can run smoothly on all implementations that comply with those configurations. Additionally, RISC-V Architecture Testing helps ensure that implementers have a correct understanding and implementation of the specification.

Through RISC-V Architecture Testing, we provide users with the assurance that the specification is correctly interpreted and that the tested implementation (DUT) complies with the guarantees of the RISC-V architecture. Only by passing the architecture test according to the RVI20 standard and obtaining approval from the RISC-V International Organization can the authorization to use the RISC-V trademark be granted in the design.

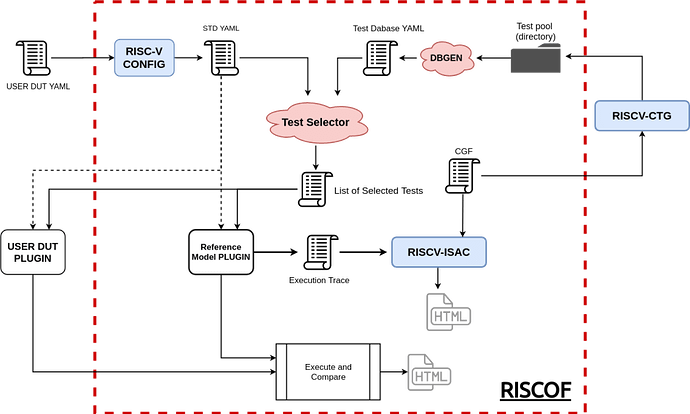

Following the process illustrated in the above diagram (see 2. Overview — RISCOF 1.23.4 documentation), StarFive has developed a YAML configuration file based on RISCV-CONFIG. This file describes the user’s input of ISA information and validates the legality of the provided register data. Furthermore, we have provided a toolchain for compiling, linking, extracting, and translating target file information for the testing framework. In addition, a Python plugin for JTAG+OpenOCD has been developed specifically for RVI20 testing of JH-7110. Through these efforts, JH-7110 has successfully passed the ACT testing according to the RVI20 standard.

The successful completion of the standard testing and recognition by the RISC-V International for JH-7110 marks an important milestone in the development of a series of JH-7110 solutions that can be regarded as RISC-V ISA compatible. We take great pride in this achievement and remain committed to delivering innovative solutions that comply with the RISC-V standard, providing customers with reliable and efficient products and services.