![]()

You can check the JH7110 datasheet for more detail:U74 MC

and the U74 document from SiFive as well: https://sifive.cdn.prismic.io/sifive/1a82e600-1f93-4f41-b2d8-86ed8b16acba_fu740-c000-manual-v1p6.pdf

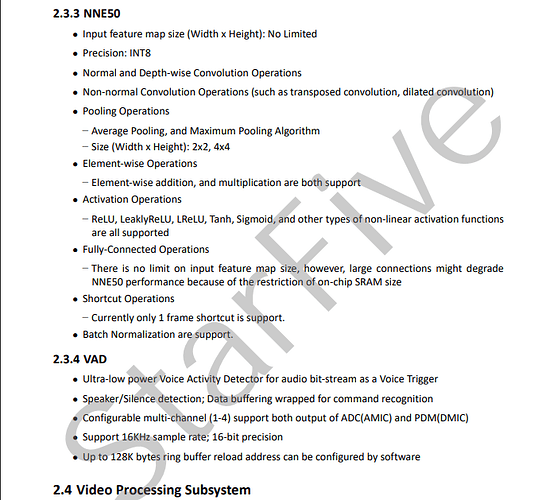

The “Vision and AI Computing” section in the JH7110 datasheet mentions “VP6”, “DLA”, “NNE50”, and “VAD”. May I know if these correspond to integrated hardware in the chip?

I think these are register names and signal names but they do not necessarily mean the correlation between JH7110 and these codenamed hardware. Currently, StarFive opens the preliminary TRM to collect feedback, you may obtain more information there.

The following assumes you’re talking about risc-v instruction set extensions.

On JH7110, you have S76 and U74

According to OpenSBI’s reporting, U74 has rv64imafdcbx.

starfive’s uboot and linux dtb announce rv64imafdc for U74 and rv64imac for S76, But I believe the bit-manipulation extension is indeed available on both U74 and S76. However, you’d better have test on specific bit-manipulation instruction to confirm its availability. (gcc 12+ supports the b extension)

If you’re using S76 core (highly unlikely), be ware that the atomic instruction support is incomplete. You can only use AMO, not LR/SC due to lacking of data cache.

Running Debian Linux, all 4 cores have the same isa display:

user@starfive1:/etc$ cat /proc/cpuinfo

processor : 0

hart : 1

isa : rv64imafdc

mmu : sv39

isa-ext :

uarch : sifive,u74-mc

64-bit

i = integer

m = multiply/divide

a = atomic

f = single floating point

d = double-precision floating point

c = compressed instructions

Is this what you’re looking for? They are elaborated in The RISC-V Reader.

I hope this helps.

rv64imafdc_zicsr_zba_zbb

For U74 core, only Zba/Zbb supported, not full bit manuplation extension is supported

thank you very much

I cannot understand it correctly.If they don’t have that, why write them? Not in this chip, at least mark it out to prompt

Hi there,

I double-checked the JH7110 datasheet but found no mention of “VP6” or “NNE50”, please let me know if I miss anything.

Oh, this should be a pretty old document, at the early stage of development, there were plans to integrate certain IPs, but some plans may have been dropped later on. Please always check the RVspace doc center for the updated document.

JH7100 != JH7110.

The SiFive U74-MC 21G1.02.00 is used inside the StarFive JH7110 SoC. I could not find a publicly available PDF document for “SiFive U74-MC Core Complex Manual 21G1.02.00”, so I am using a “SiFive U74-MC Core Complex Manual 21G1.01.00” document for my reference and in Chapter 7 “Custom Instructions and CSRs” it lists the following custom instructions:

7.1 CFLUSH.D.L1 (Only available in M-mode)

7.2 CDISCARD.D.L1 (Only available in M-mode)

7.3 CEASE (Privileged instruction only available in M-mode)

7.4 PAUSE

7.5 Branch Prediction Mode CSR (M-mode CSR)

7.6 SiFive Feature Disable CSR (M-mode CSR)

Any mention of “x” would probably be in reference to the above four custom SiFive instructions and the two custom Control and Status Registers.

There is also an optional “SiFive Custom Instruction Extension (SCIE)” which may or may not be present in the JH7110. This would typically be added for 1 to 2 cycle custom instructions.

Ah, Ha, that was the JH7100 datasheet. Sorry, we were not on the same page. Since JH7100 is not a mass-produced product, our main support effort was not there, so this may be the cause of the misunderstanding.

Yes, then you are correct, NNE50 and VP6 are exactly the adopted IP code names for JH7100.