- "u1_reset_ctrl_clk_src", "osc", 0, 1, 1);

- priv->pll[PLL_OF(JH7110_DDR_ROOT)] =

- devm_clk_hw_register_fixed_factor(priv->dev,

- "ddr_root", "pll1_out", 0, 1, 1);

- priv->pll[PLL_OF(JH7110_VDEC_ROOT)] =

- devm_clk_hw_register_fixed_factor(priv->dev,

- "vdec_root", "pll0_out", 0, 1, 1);

- priv->pll[PLL_OF(JH7110_VENC_ROOT)] =

- devm_clk_hw_register_fixed_factor(priv->dev,

- "venc_root", "pll2_out", 0, 1, 1);

- priv->pll[PLL_OF(JH7110_VOUT_ROOT)] =

- devm_clk_hw_register_fixed_factor(priv->dev,

- "vout_root", "pll2_out", 0, 1, 1);

- priv->pll[PLL_OF(JH7110_GMACUSB_ROOT)] =

- devm_clk_hw_register_fixed_factor(priv->dev,

- "gmacusb_root", "pll0_out", 0, 1, 1);

- priv->pll[PLL_OF(JH7110_PCLK2_MUX_FUNC_PCLK)] =

- devm_clk_hw_register_fixed_factor(priv->dev,

- "u2_pclk_mux_func_pclk", "apb_bus_func", 0, 1, 1);

- priv->pll[PLL_OF(JH7110_PCLK2_MUX_BIST_PCLK)] =

- devm_clk_hw_register_fixed_factor(priv->dev,

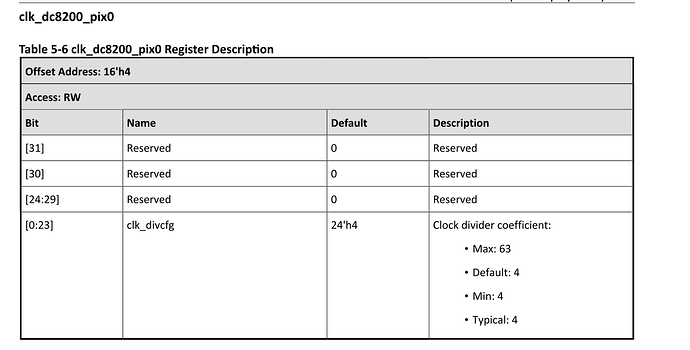

![]() 。往offset 0x04写入8即可,目前测试问题已经解决了。

。往offset 0x04写入8即可,目前测试问题已经解决了。